# **Synchronous Rectifier**

SOP-8

## CD9356F

SOP-8 Surface Mount Plastic Package RoHS compliant

### **GENERAL DESCRIPTION**

CD9356F is a smart secondary-side switch IC designed for isolated fly-back system. The IC emulate the behavior of Schottky diode rectifier for reduce power dissipation. CD9356F works on CCM/DCM and QR operation modes. Ruggedness and noise immunity are accomplished using an advance blanking scheme and double-pulse suppression which allow reliable operation in all operating modes. CD9356F senses the build-in MOSFET drain-source voltage and output ideal drive signal with less external components. It can support wide range of system output voltage 5V~12V

### **FEATURES:**

- 1. Build-in  $11m\Omega$  100V MOSFET

- 2. Low current consumption

- 3. Up to 150KHz operation frequency

- 4. 30ns turn-off propagation delay

- 5. VCC Operation 4.5V to 30V

- 6. CCM DCM and QR operation

- 7. SOP8 Package

#### APPLICATIONS:

- 1. 5V/9V/12V AC-DC adaptor

- 2. 18W PD/QC Charger systems

- 3. High Energy Efficiency systems

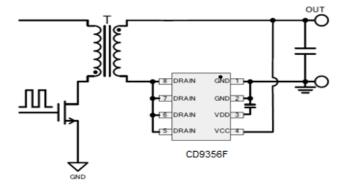

## **Simplified Application Circuit**

Low-side Application Figure 1. Simplified Application of CD9356F

# **Pin Function Description**

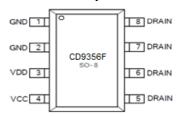

Figure 2. Pin Configuration

| Pin No. | Pin Name | Description                                     |

|---------|----------|-------------------------------------------------|

| 1,2     | GND      | Power Ground, Return for MOSFET Source          |

| 3       | VDD      | Inner Power Supply, Connect Capacitor to Ground |

| 4       | VCC      | Out Power Supply                                |

| 5.6,7,8 | DRAIN    | MOSFET Drain                                    |

# **Package Dissipation Rating**

| Package | θ <sub>JC</sub> (°C/W) | θ <sub>JA</sub> (°C/W) |  |

|---------|------------------------|------------------------|--|

| SOP-8   | 50                     | 130                    |  |

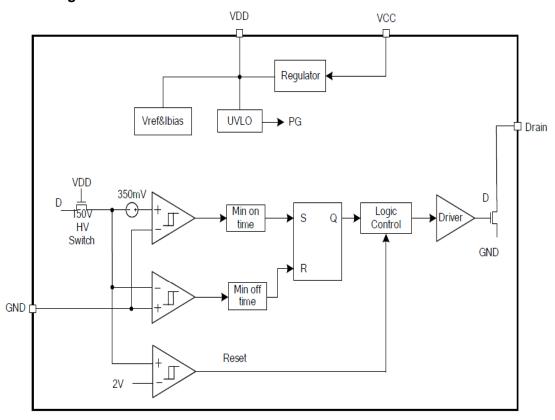

# **Block Diagram**

Figure 3.Block diagram of CD9356F

## **ABSOLUTE MAXIMUM RATINGS** (T<sub>A</sub>=25°C Unless otherwise specified)

| Parameters                           | Symbol           | Rating     | Unit |

|--------------------------------------|------------------|------------|------|

| MOSFET Drain                         | DRAIN            | -1 to 100  | V    |

| VCC Input Voltage                    | VCC              | -0.3 to 36 | V    |

| Operating Junction Temperature       | $T_J$            | -40 to 125 |      |

| Min/Max Storage Temperature          | T <sub>STG</sub> | -55 to 150 | °C   |

| Lead Temperature (Soldering. 10secs) | T <sub>L</sub>   | 260        |      |

#### Notes:

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions are not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability

## **Recommended Operating Conditions**

| Description          | Symbol | Values   | Unit |  |

|----------------------|--------|----------|------|--|

| VCC Supply Voltage   | VCC    | 4.5~30   | V    |  |

| VCC bypass capacitor | VCC    | 1        | uF   |  |

| Switch Frequency     | $F_sw$ | <150     | KHz  |  |

| MOSFET Drain Voltage | DRAIN  | -0.6~100 | V    |  |

**ELECTRIC CHARACTERISTICS** (VCC = 12V, T<sub>A</sub> = +25°C, unless otherwise specified)

| Parameter                            | Symbol                | Test Condition    | Min | Тур | Max | Unit |

|--------------------------------------|-----------------------|-------------------|-----|-----|-----|------|

| VCC Section                          |                       |                   |     |     |     |      |

| Quiescent Current                    | ICC                   |                   |     | 600 |     | uA   |

| VCC ON Voltage                       | V <sub>CC_ON</sub>    | VCC Going Up      |     | 4.2 |     |      |

| VCC OFF Voltage                      | $V_{CC\_OFF}$         | VCC Going Down    | -   | 3.8 |     | V    |

| VCC clamp voltage                    | V <sub>CC_clamp</sub> |                   |     | 32  |     |      |

| VDD Section                          |                       |                   |     |     |     |      |

| VDD Operation Range                  | $VDD_{RANGE}$         | VCC=OPEN          | 4.0 |     | 6.5 | V    |

|                                      | $VDD_{RATED}$         | VCC=5~15V         | 5.0 | 6.5 | 7   | V    |

|                                      | $I_{VDDQ}$            | VDD=5V,Drain=OPEN |     | 600 |     | uA   |

|                                      | VDD <sub>UVP</sub>    | VDD from 7V to 0V |     | 3.8 |     | mV   |

|                                      | I <sub>VDDC</sub>     |                   |     | 30  |     | mA   |

| MOS Section                          |                       |                   |     |     |     |      |

| Static drain to source on resistance | R <sub>DSON</sub>     | VCC=10V           |     | 11  |     | mΩ   |

|                                      | VBSS                  | ld=100uA          | 100 |     |     | V    |

|                                      | T_r                   | 0→20V,IO=3A       |     | 20  |     | nS   |

|                                      | T_f                   | 20V→0V,IO=3A      |     | 50  |     | nS   |

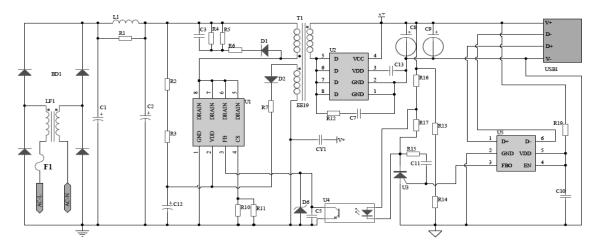

# **Typical Application Example**

Figure.3 Schematic of Typical Application Circuit

### **Functional Description**

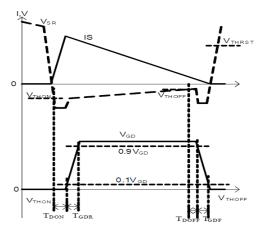

CD9356F detects the internal MOSFET voltage (VDS). When the drain voltage is lower than the turn-on threshold voltage (VTHON), it outputs a positive drive voltage after a turn-on delay time internal MOSFET will turn on and the current will transfer from the body diode into the internal channel, then lower conduction loss can be achieved. In the process of internal MOSFET decreasing linearly toward zero, the drain rises synchronically. When it rises over the turn off threshold voltage (VTHOFF), CD9356F internal MOSFET gate voltage to zero delay time (TDOFF). See Figure.4

Figure 4. Typical Waveforms of CD9356F

## **Power Supply**

The IC supply voltage is monitored by the under lockout circuit. It is possible to turn off the IC by pulling VDD pin below the minimum turn off threshold voltage, without damaging the IC. To prevent noise problems, a bypass ceramic capacitor connected to VDD and GND should be placed as close as possible to IC.

#### **UVLO Mode**

The IC remains in the UVLO condition until the voltage on the VDD pin exceeds the VDD turn on threshold voltage VDD\_ON. During the time the IC remains in the UVLO state, the gate drive circuit is inactive and the IC draws a quiescent current of ICC START. The UVLO mode is accessible from any other state of operation whenever the IC supply voltage condition of VDD < VDD\_OFF occurs.

### **Drain Voltage Inner Sense**

DRAIN pin is used to sense the internal MOSFET Drain voltage. This is a high voltage pin and particular care must be taken in properly routing the connection to the internal MOSFET drain side.

#### **MOT Protection Mode**

If the secondary current conduction time is shorter than the MOT (Minimum On driver output is disabled. This function can avoid reverse current that occurs when the system works at very low duty-cycles or at very light/no load conditions and reduce system standby power consumption by disabling GATE outputs. The Cycle by Cycle MOT Check circuit is always activated under Normal Mode and MOT that the IC can automatically resume normal operation once the load increases to a level current conduction time is longer than MOT.

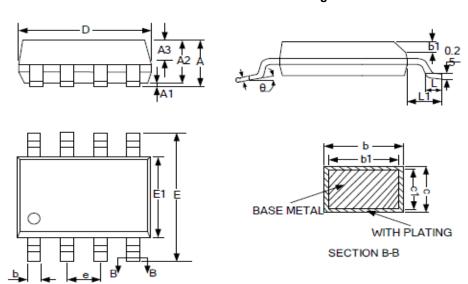

# **Package Details**

## **SOP-8 Surface Mount Plastic Package**

| SYMBOL  | MILLIMETER SYMBOL MILLIMETER |      |      |        | R       |      |      |

|---------|------------------------------|------|------|--------|---------|------|------|

| STWIBOL | MIN                          | NOM  | MAX  | STMBOL | MIN     | NOM  | MAX  |

| Α       | _                            | _    | 1.75 | D      | 4.70    | 4.90 | 5.10 |

| A1      | 0.05                         | _    | 0.15 | E      | 5.80    | 6.00 | 6.20 |

| A2      | 1.30                         | 1.40 | 1.50 | E1     | 3.70    | 3.90 | 4.10 |

| A3      | 0.60                         | 0.65 | 0.70 | е      | 1.27BSC |      |      |

| b       | 0.39                         | _    | 0.48 | h      | 0.25    | _    | 0.50 |

| b1      | 0.38                         | 0.41 | 0.43 | L      | 0.50    | _    | 0.80 |

| С       | 0.21                         | _    | 0.26 | L1     | 1.05BSC |      |      |

| c1      | 0.19                         | 0.20 | 0.21 | θ      | 0       | _    | 8°   |

# **Ordering and Marking Information**

| Part Number | Package Description |  |  |

|-------------|---------------------|--|--|

| CD9356F     | SOP-8               |  |  |

## **Recommended Product Storage Environment for Discrete Semiconductor Devices**

This storage environment assumes that the Diodes and transistors are packed properly inside the original packing supplied by CDIL.

- · Temperature 5 °C to 30 °C

- · Humidity between 40 to 70 %RH

- · Air should be clean.

- · Avoid harmful gas or dust.

- · Avoid outdoor exposure or storage in areas subject to rain or water spraying .

- · Avoid storage in areas subject to corrosive gas or dust. Product shall not be stored in areas exposed to direct sunlight.

- · Avoid rapid change of temperature.

- · Avoid condensation.

- · Mechanical stress such as vibration and impact shall be avoided.

- · The product shall not be placed directly on the floor.

- · The product shall be stored on a plane area. They should not be turned upside down. They should not be placed against the wall.

### **Shelf Life of CDIL Products**

The shelf life of products is the period from product manufacture to shipment to customers. The product can be unconditionally shipped within this period. The period is defined as 2 years.

If products are stored longer than the shelf life of 2 years the products shall be subjected to quality check as per CDIL quality procedure.

The products are further warranted for another one year after the date of shipment subject to the above conditions in CDIL original packing.

### Floor Life of CDIL Products and MSL Level

When the products are opened from the original packing, the floor life will start.

For this, the following JEDEC table may be referred:

| JEDEC MSL Level |                    |                 |  |  |  |

|-----------------|--------------------|-----------------|--|--|--|

| Level           | Time               | Condition       |  |  |  |

| 1               | Unlimited          | ≤30 °C / 85% RH |  |  |  |

| 2               | 1 Year             | ≤30 °C / 60% RH |  |  |  |

| 2a              | 4 Weeks            | ≤30 °C / 60% RH |  |  |  |

| 3               | 168 Hours          | ≤30 °C / 60% RH |  |  |  |

| 4               | 72 Hours           | ≤30 °C / 60% RH |  |  |  |

| 5               | 48 Hours           | ≤30 °C / 60% RH |  |  |  |

| 5а              | 24 Hours           | ≤30 °C / 60% RH |  |  |  |

| 6               | Time on Label(TOL) | ≤30 °C / 60% RH |  |  |  |

#### **Customer Notes**

#### **Component Disposal Instructions**

- 1. CDIL Semiconductor Devices are RoHS compliant, customers are requested to please dispose as per prevailing Environmental Legislation of their Country.

- 2. In Europe, please dispose as per EU Directive 2002/96/EC on Waste Electrical and Electronic Equipment (WEEE).

### **Disclaimer**

The product information and the selection guides facilitate selection of the CDIL's Semiconductor Device(s) best suited for application in your product(s) as per your requirement. It is recommended that you completely review our Data Sheet(s) so as to confirm that the Device(s) meet functionality parameters for your application. The information furnished in the Data Sheet and on the CDIL Web Site/CD are believed to be accurate and reliable. CDIL however, does not assume responsibility for inaccuracies or incomplete information. Furthermore, CDIL does not assume liability whatsoever, arising out of the application or use of any CDIL product; neither does it convey any license under its patent rights nor rights of others. These products are not designed for use in life saving/support appliances or systems. CDIL customers selling these products (either as individual Semiconductor Devices or incorporated in their end products), in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damages resulting from such sale(s).

CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.

CDIL is a registered trademark of

#### **Continental Device India Pvt. Limited**